参考:UG1181 Zynq-7000 Programable Soc Architrcture Porting Quick Start Guide

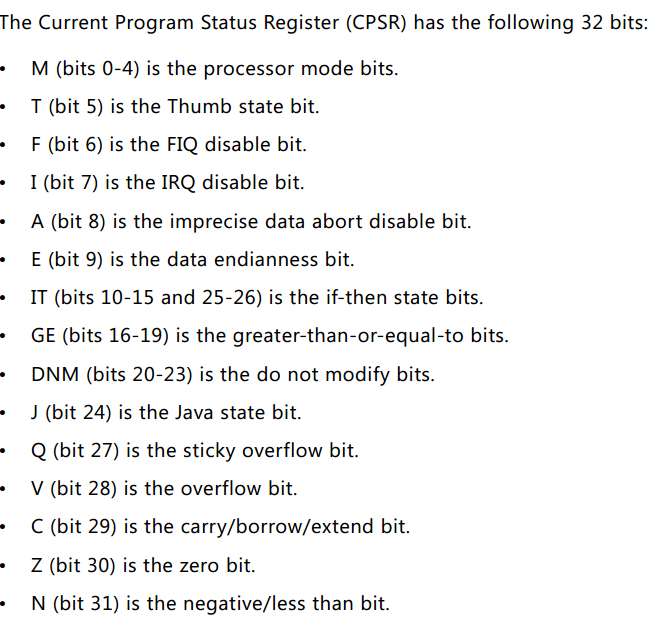

zynq处理器结构图

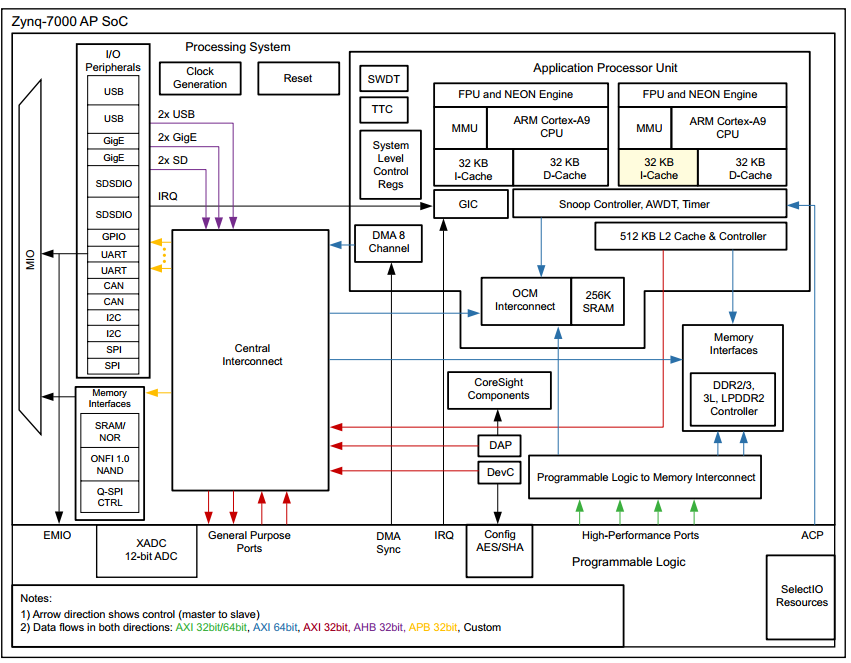

CPU MODE:At any given time, the CPU can be in only one mode, but it can switch modes due to external events (interrupts) or programmatically (对比ARM里的7种模式)

User Mode 用户模式

FIQ Mode 快速中断模式

IRQ Mode 中断模式

SVC Mode

ABORT mode

undefined mode

system mode

monitor mode

Hyp mode

trust zone技术简介:

目前的一些安全手段。

CPU通过内存映射手段给每个进程营造一个单独的地址空间来隔离多个进程的代码和数据,通过内核空间和用户空间不同的特权级来隔离操作系统和用户进程的代码和数据。但由于内存中的代码和数据都是明文,容易被同处于内存中的其它应用偷窥,因此出现了扩展的安全模块,应用将加密数据送往安全模块,由安全模块处理完后再返回结果给相应的应用。

很多消费电子设备都使用扩展的安全模块来确保数据安全,目前常见的方式有:

外部挂接硬件安全模块

数据的处理交由外部的安全模块实现,这些模块能够保护自己的资源和密钥等数据的安全,如SIM卡、各种智能卡或连接到外部的硬件加解密模块等,但其同主芯片的通信线路暴露在外部,容易被监听破解。另外,通信的速率比较低。

内部集成硬件安全模块

将外部安全模块的功能集成到芯片内,因此一个芯片上至少有两个核:一个普通核和一个安全核。优点是核与核之间的通信在芯片内部实现,不再暴露在外面。缺点是核之间的通信速度仍然较低,而且单独的安全核性能有限,还会会占用SoC面积,成本较高。

TrustZone是ARM针对消费电子设备设计的一种硬件架构,其目的是为消费电子产品构建一个安全框架来抵御各种可能的攻击。

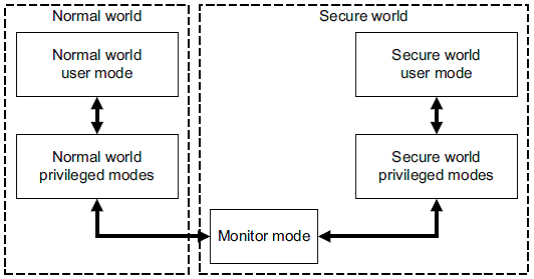

TrustZone在概念上将SoC的硬件和软件资源划分为安全(Secure World)和非安全(Normal World)两个世界,所有需要保密的操作在安全世界执行(如指纹识别、密码处理、数据加解密、安全认证等),其余操作在非安全世界执行(如用户操作系统、各种应用程序等),安全世界和非安全世界通过一个名为Monitor Mode的模式进行转换

图1. ARM的安全世界和非安全世界

处理器架构上,TrustZone将每个物理核虚拟为两个核,一个非安全核(Non-secure Core, NS Core),运行非安全世界的代码;和另一个安全核(Secure Core),运行安全世界的代码。

两个虚拟的核以基于时间片的方式运行,根据需要实时占用物理核,并通过Monitor Mode在安全世界和非安全世界之间切换,类似同一CPU下的多应用程序环境,不同的是多应用程序环境下操作系统实现的是进程间切换,而Trustzone下的Monitor Mode实现了同一CPU上两个操作系统间的切换。

两个独立的 ARM Cortex-A9(ARMv7)处理器内核与两个Neon 协处理器,他们共享512KB 的L2 缓存。各处理的L1 级缓存是独立的,因此两个处理器可以单独运行各自的任务。Neon技术主要用于加速多媒体和信号处理算法(如视频编解码、3D图形、图像处理技术、游戏加速等),Neon可认为是128bit矢量DSP,可执行打包的SIMD 指令,最高支持64bit单精度浮点运算。

Thumb2指令设置,NEON技术,增强型SIMD,一次指令可以处理多个数据。VFPU vector floating point unit向量浮点单元

Caches: L1 和L2 级Cache。512KB L2 级Cache为两个处理器共有,32KB D-Cache 和 I-Cache 为每个处理器私有。

8 通道 DMA 控制器。64bit位宽,支持 M-toM,其中四个通道支持 PL请求。

GIC(Generic Interrupt Controller)。管理95 中断信号,需要注意的是,PL-PS 的中断有对应各自处理器的快速中断和普通的F2P IRQ。

侦听控制单元(SCU)。智能管理两个出来器与 L2 共享高速缓存之间的数据一致性。

OCM(On Chip Memory)。256KB SRAM,PL可以通过 AXI_HP 接口直接访问。

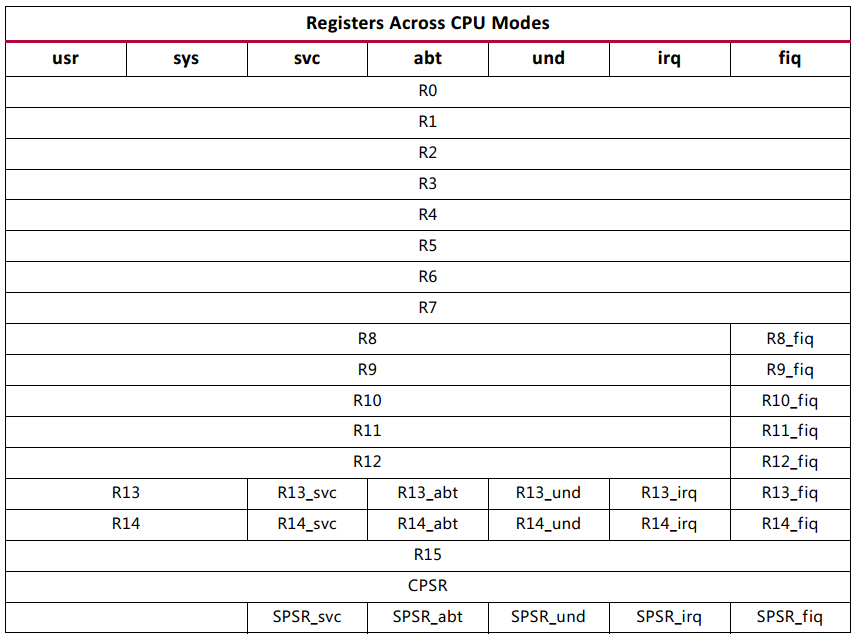

寄存器设置: